Page 59 고등학교 디지털 논리 회로 교과서

P. 59

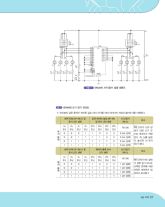

VCC

S 1 S 2

DIP DIP

SW-4 SW-4

24

8 4 2 1 8 9 1 2 4 8

7 A0 VCC I/O 0 10

6 A1 I/O 1 11

5 A2 I/O 2 13

4 A3 I/O 3 14 +

A 3 A0 3 A4 I/O 4 15 I/O 0 I/O 3 - 5V

A2 A1 2 A5 I/O 5 16 I/O 1 I/O 2

1 A6 I/O 6 17

23 A7 I/O 7

22 A8

19 A9

D1 D2 D3 D4 D 5 D 6 D 7 D 8

R 5 A10

1K

18 CS

20 OE

21

R 1 R 2 R 3 R 4 WE R 6 R 7 R 8 R 9

1K 1K 1K 1K GND 1K 1K 1K 1K

S3 12

HY6116ALP-10

PB

SW

GND

그림 1 SRAM의 쓰기/읽기 실험 회로도

표 1 SRAM의 쓰기 읽기 진리표

※ 진리표와 같은 동작이 되도록 실습 따라 하기를 하며 데이터의 저장과 불러오기를 이해한다.

번지 지정 DIP SW S1 및 입력 데이터 설정 DIP SW 쓰기/읽기 비고

표시 LED 상태 및 표시 LED 상태 SW S3

A3 A2 A1 A0 I/O3 I/O2 I/O1 I/O0

PB SW WE 단자가 L(0) 상

(D1) (D2) (D3) (D4) (D8) (D7) (D6) (D5)

쓰 태가 되면 쓰기 모

기 0 0 0 1 1 0 0 0 0 (on 상태) 드로 데이터가 저장

동 0 0 1 1 1 1 0 0 0 (on 상태) 된다. 즉, S3를 눌렀

작

0 1 1 1 1 1 1 0 0 (on 상태) 다 놓으면 쓰기(저

장)가 된다.

1 1 1 1 1 1 1 1 0 (on 상태)

번지 선택 DIP SW S1 및 데이터 출력 표시 쓰기/읽기 비고

표시 LED 상태 LED 상태 SW S3

A3 A2 A1 A 0 I/O3 I/O2 I/O1 I/O0

PB SW

(D1) (D2) (D3) (D 4 ) (D8) (D7) (D6) (D5) WE 단자가 H(1) 상태

읽 가 되면 읽기 모드로

기 0 0 0 1 1 0 0 0 1 (off 상태)

선택된 번지에 저장

동 0 0 1 1 1 1 0 0 1 (off 상태)

작 되었던 데이터가 읽

0 1 1 1 1 1 1 0 1 (off 상태)

혀져서 표시된다.

1 1 1 1 1 1 1 1 1 (off 상태)

실습 과제 57